tokensonly.com 2010

special thanks to plool

# Gun Fight Computer Service Manual

# For The Midway 8080 Microprocessor Game Series

A comprehensive analysis of the Gun Fight game computer.

Technical Production by Laurel Publications

© 1976 Kush N' Stuff Amusement Electronics, Inc.

tekensenly.com 2010

# **Table of Contents**

|     | SI           | ECTION 1 GENERAL INFORMATION       |

|-----|--------------|------------------------------------|

| 1.1 | Introduction | on                                 |

|     | 1.1.1        | Why Use A Microprocessor?          |

|     | 1.1.2        | Random Logic Vs. Processor Control |

|     | 1.1.3        | Advantages Of Software             |

| 1.2 | A Typical    | Game Sequence                      |

|     | 1.2.1        | The Attract Mode                   |

|     | 1.2.2        | The Credit Mode                    |

|     | 1.2.3        | The Play Mode                      |

| 1.3 | Electrical   | Adjustments                        |

|     | 1.3.1        | Introduction                       |

|     | 1.3.2        | TV Monitor Adjustments             |

|     | 1.3.3        | Power Supply Adjustments           |

|     | 1.3.4        | Operator Adjustments               |

|     | 1.3.5        | Sound System Adjustments           |

| 1.4 | System Ar    | chitecture                         |

|     | 1.4.1        | System Subassemblies               |

|     | 1.4.2        | Signal Flow                        |

|     | 1.4.3        | Multiplex Data Bus                 |

|     | 1.4.4        | Output Data Bus                    |

|     | 1.4.5        | Address Bus                        |

|     | 1.4.6        | The Sample Line                    |

|     | 1.4.7        | The Reset Line                     |

| 1.5 | Mother PC    | B Architecture                     |

|     | 1.5.1        | Introduction                       |

|     | 1.5.2        | Sync And Timing                    |

|     | 1.5.3        | The RAM Memory                     |

|     | 1.5.4        | RAM Data Latches                   |

|     | 1.5.5        | Video Output                       |

|     | 1.5.6        | CPU Input Selector                 |

|     | 1.5.7        | I/O Drivers                        |

|     | 1.5.8        | The Status Latch                   |

|     | 1.5.9        | Interrupt Flip-flop                |

|     | 1.5.10       | The ROM Selector                   |

|     | 1.5.11       | The ROM Memory                     |

|     | 1.5.12       | The 8080 CPU                       |

| 1.6 | Game PCB     | Architecture                       |

|     | 1.6.1        | General Functions                  |

|     | 1.6.2        | Player Controls                    |

|     | 1.6.3        | The Opto-isolators                 |

|     | 1.6.4        | Operator Instructions              |

|     | 1.6.5        | The Multiplexers                   |

|     | 1.6.6        | The Latches                        |

|     | 1.6.7        | The Shifter                        |

| 1.7 |           | Of Specific Game PCB Components        |

|-----|-----------|----------------------------------------|

|     | 1.7.1     | Introduction                           |

|     | 1.7.2     | The Opto-isolators                     |

|     | 1.7.3     | The Schmitt Triggers                   |

|     | 1.7.4     | The Multiplexers                       |

|     | 1.7.5     | The Latches                            |

|     | 1.7.6     | The Data Shifters                      |

|     | 1.7.7     | The Decoder                            |

|     |           |                                        |

|     | S         | ECTION 2 THEORY OF OPERATION           |

| 2.1 | The Power | Supplies11                             |

|     |           | Introduction                           |

|     | 2.1.2     |                                        |

|     | 2.1.3     |                                        |

|     | 2.1.4     | The +12 Volt Source                    |

|     | 2.1.5     | The +5 Volt Source                     |

|     | 2.1.6     | The -5 Volt Source                     |

|     | 2.1.7     | The Reset Line                         |

|     | 2.1.8     | The Lamp Supplies                      |

|     | 2.1.0     | The Europe Supplies                    |

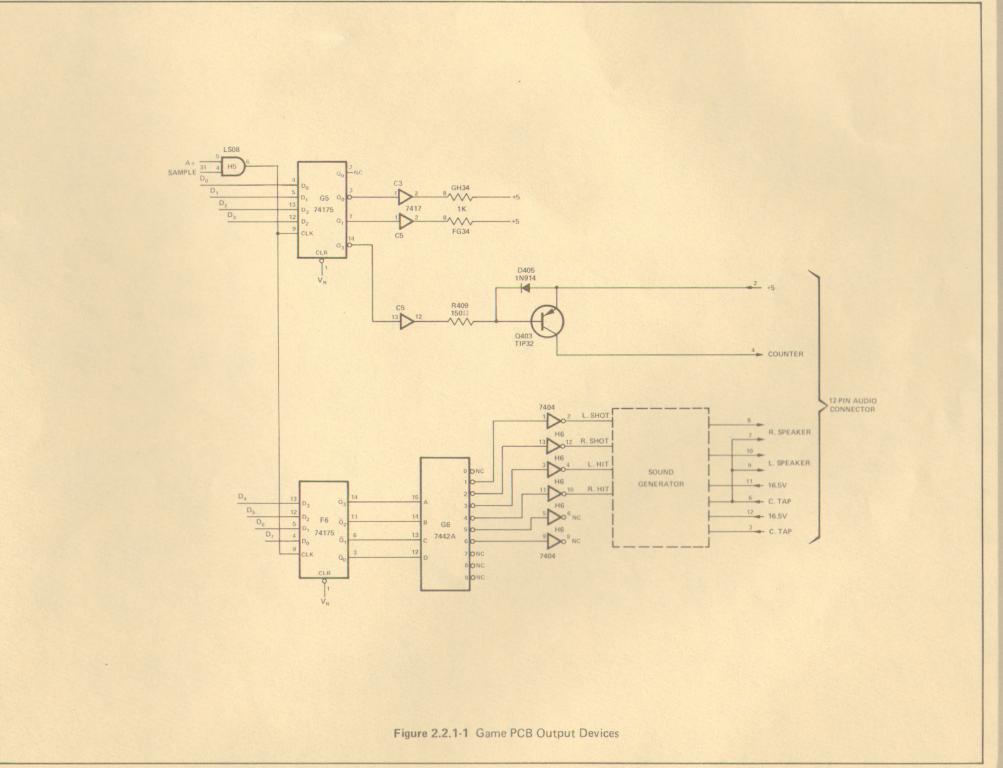

| 2.2 | Operation | Of The Game PCB Digital Circuitry      |

|     | 2.2.1     | Introduction                           |

|     | 2.2.2     | The Game PCB As An Output Peripheral   |

|     | 2.2.3     | The Output Data Latches                |

|     | 2.2.4     | Decode And Interface                   |

|     | 2.2.5     | Video Data And CRT Motion              |

|     | 2.2.6     | Shifter Circuit Logic                  |

|     | 2.2.7     | A Typical Shifter Sequence             |

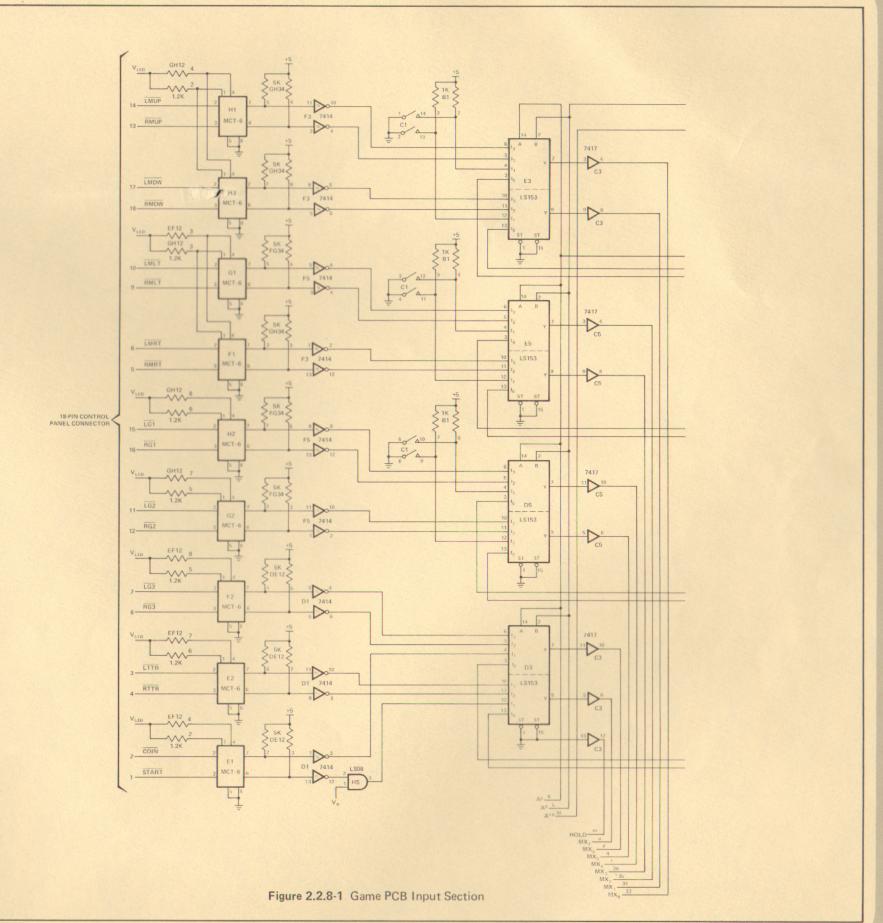

|     | 2.2.8     | Multiplexed Game Data                  |

|     | 2.2.9     | The Player Control Inputs              |

|     | 2.2.10    | Game Data Multiplexers                 |

|     |           | 40                                     |

| 2.3 |           | d Circuitry                            |

|     | 2.3.1     |                                        |

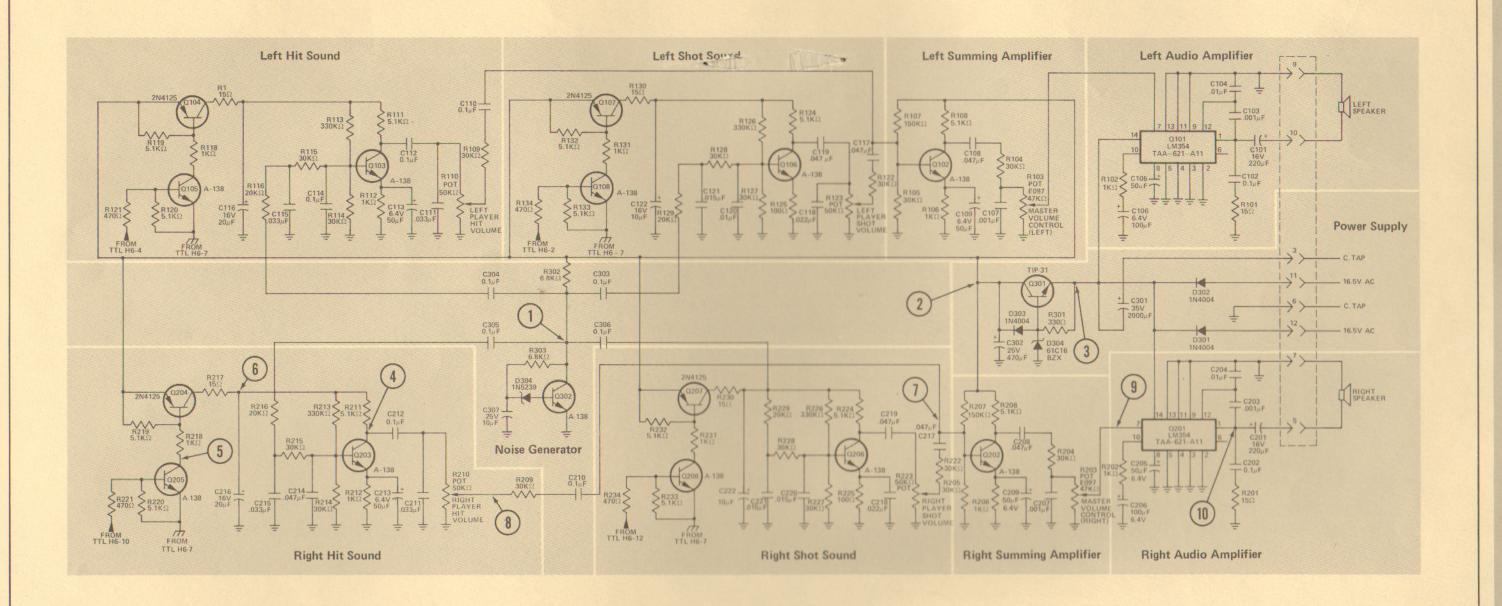

|     |           | Power Control And Raw Noise Generation |

|     | 2.3.3     | Generation Of The Right Hit Sound      |

|     | 05051     | ON A TROUBLESHOOTING PROOFFILIPES      |

|     | SECTI     | ON 3 TROUBLESHOOTING PROCEDURES        |

| 3.1 | Introduct | ion                                    |

| 3.2 | Control   | ignal Procedures                       |

| 3.2 | 3.2.1     |                                        |

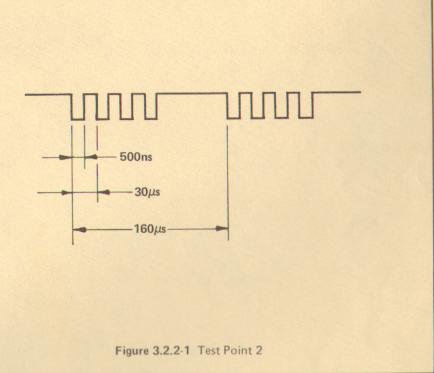

|     |           | Test Point 2                           |

|     |           | Test Point 2                           |

|     |           |                                        |

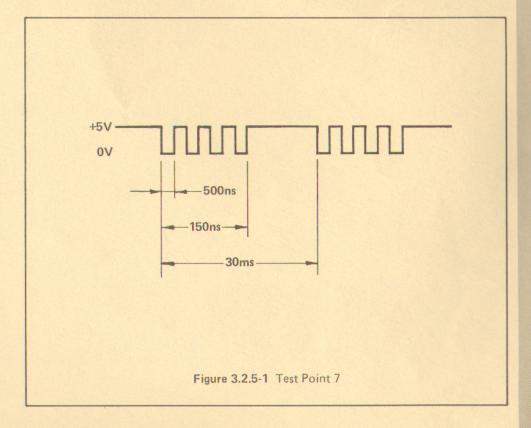

|     |           | Test Points 4, 5 & 6 Test Point 7      |

|     |           |                                        |

|     | 3.2.6     | Test Points 8, 9 & 10                  |

| Attract Mode Display                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3.3    | Data Bus Procedures        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------|

| 1.2.1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.4    | Shifter Procedures         |

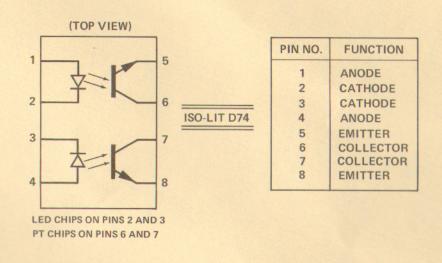

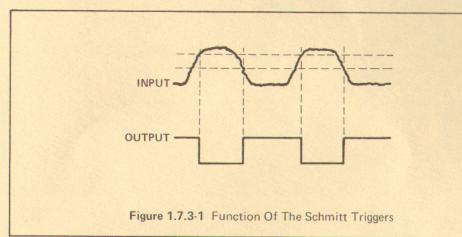

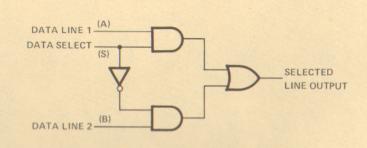

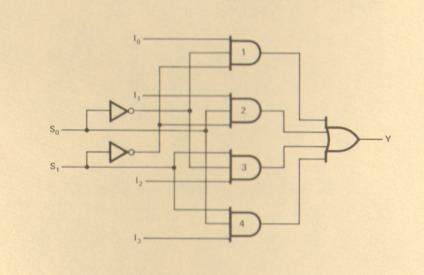

| 1.2.1-1       Attract Mode Display       .2         1.2.2-1       Credit Mode Display       .2         1.2.3-2       Final Play Mode Display       .2         1.2.3-2       Final Play Mode Display       .2         1.3.3-1       Power Supply Adjustments       .3         1.3.5-1       Sound And Coins/Plays/Time Adjustments       .3         1.4.1-1       System Block Diagram       .4         1.5.1-1       Mother PCB Block Diagram       .5         1.5.12-1       8080 CPU Block Diagram       .5         1.5.12-1       8080 CPU Block Diagram       .6         1.6.1-1       Game PCB Block Diagram       .6         1.6.1-1       Game PCB Block Diagram       .7         1.6.2-1       Gun Arm Angle Code       .7         1.6.2-1       Word Locations During Shift.       .8         1.6.7-2       Shift Process As Viewed On CRT       .8         1.6.7-2       Shift Process As Viewed On CRT       .8         1.7.2-1       Opto-isolator Information       .9         1.7.3-1       Function Of The Schmitt Triggers       .10         1.7.4-1       Basic Multiplexer Logic Diagram       .10         1.7.4-2       Four-input Multiplexer Logic Diagram       .10                                               | 3.5    | Sound System Procedures    |

| 1.2.1-1       Attract Mode Display       .2         1.2.2-1       Credit Mode Display       .2         1.2.3-2       Final Play Mode Display       .2         1.2.3-2       Final Play Mode Display       .2         1.3.3-1       Power Supply Adjustments       .3         1.3.5-1       Sound And Coins/Plays/Time Adjustments       .3         1.4.1-1       System Block Diagram       .4         1.5.1-1       Mother PCB Block Diagram       .5         1.5.12-1       8080 CPU Block Diagram       .5         1.5.12-1       8080 CPU Block Diagram       .6         1.6.1-1       Game PCB Block Diagram       .6         1.6.1-1       Game PCB Block Diagram       .7         1.6.2-1       Gun Arm Angle Code       .7         1.6.2-1       Word Locations During Shift.       .8         1.6.7-2       Shift Process As Viewed On CRT       .8         1.6.7-2       Shift Process As Viewed On CRT       .8         1.7.2-1       Opto-isolator Information       .9         1.7.3-1       Function Of The Schmitt Triggers       .10         1.7.4-1       Basic Multiplexer Logic Diagram       .10         1.7.4-2       Four-input Multiplexer Logic Diagram       .10                                               |        |                            |

| 1.2.2-1       Credit Mode Display       .2         1.2.3-2       Final Play Mode Display       .2         1.3.3-1       Power Supply Adjustments       .3         1.3.5-1       Sound And Coins/Plays/Time Adjustments       .3         1.3.5-1       Sound And Coins/Plays/Time Adjustments       .3         1.4.1-1       System Block Diagram       .4         1.5.1-1       Mother PCB Block Diagram       .5         1.5.12-1       8080 CPU Block Diagram       .6         1.6.1-1       Game PCB Block Diagram       .7         1.6.2-1       Gun Arm Angle Code       .7         1.6.7-1       Word Locations During Shift       .8         1.6.7-2       Shift Process As Viewed On CRT       .8         1.7.2-1       Opto-isolator Information       .9         1.7.3-1       Function Of The Schmitt Triggers       .10         1.7.4-1       Basic Multiplexer Logic Diagram       .10         1.7.4-2       Four-input Multiplexer Logic Diagram       .10         1.7.5-1       74175 Quad Latch Logic Diagram       .10         1.7.6-2       25S10 Data Shifter Pin Configuration       .11         1.7.6-1       25S10 Data Shifter Pin Configuration       .11         1.7.7-1       7442 Decod                      |        | LIST OF ILLUSTRATIONS      |

| 1.2.3-1       Initial Play Mode Display       .2         1.2.3-2       Final Play Mode Display       .2         1.3.3-1       Power Supply Adjustments       .3         1.3.5-1       Sound And Coins/Plays/Time Adjustments       .3         1.3.5-1       System Block Diagram       .4         1.5.1-1       Mother PCB Block Diagram       .5         1.5.12-1       8080 CPU Block Diagram       .6         1.6.1-1       Game PCB Block Diagram       .7         1.6.2-1       Gun Arm Angle Code       .7         1.6.7-1       Word Locations During Shift       .8         1.6.7-2       Shift Process As Viewed On CRT       .8         1.7.2-1       Opto-isolator Information       .9         1.7.3-1       Function Of The Schmitt Triggers       .10         1.7.4-1       Basic Multiplexer Logic Diagram       .10         1.7.4-2       Four-input Multiplexer Logic Diagram       .10         1.7.5-1       74175 Quad Latch Logic Diagram       .10         1.7.6-2       25S10 Data Shifter Pin Configuration       .11         1.7.6-2       25S10 Truth Table       .11         1.7.7-1       7442 Decoder Logic Diagram       .11         1.7.7-2       7442 Decoder Logic Diagram                              | 1.2.1- | Attract Mode Display       |

| 1.2.3-2       Final Play Mode Display       .2         1.3.3-1       Power Supply Adjustments       .3         1.3.5-1       Sound And Coins/Plays/Time Adjustments       .3         1.4.1-1       System Block Diagram       .4         1.5.1-1       Mother PCB Block Diagram       .5         1.5.1-2-1       8080 CPU Block Diagram       .6         1.6.1-1       Game PCB Block Diagram       .7         1.6.2-1       Gun Arm Angle Code       .7         1.6.7-1       Word Locations During Shift       .8         1.6.7-2       Shift Process As Viewed On CRT       .8         1.7.2-1       Opto-isolator Information       .9         1.7.3-1       Function Of The Schmitt Triggers       .10         1.7.4-1       Basic Multiplexer Logic Diagram       .10         1.7.4-2       Four-input Multiplexer Logic Diagram       .10         1.7.5-1       74175 Quad Latch Logic Diagram       .10         1.7.6-1       25S10 Data Shifter Pin Configuration       .11         1.7.6-2       25S10 Truth Table       .11         1.7.7-1       7442 Decoder Logic Diagram       .11         1.7.7-1       7442 Decoder Logic Diagram       .11         2.2.1-1       Game PCB Output Devices                              | 1.2.2- |                            |

| 1.3.3-1       Power Supply Adjustments       .3         1.3.5-1       Sound And Coins/Plays/Time Adjustments       .3         1.4.1-1       System Block Diagram       .4         1.5.1-1       Mother PCB Block Diagram       .5         1.5.12-1       8080 CPU Block Diagram       .6         1.6.1-1       Game PCB Block Diagram       .7         1.6.2-1       Gun Arm Angle Code       .7         1.6.7-1       Word Locations During Shift       .8         1.6.7-2       Shift Process As Viewed On CRT       .8         1.6.7-2       Shift Process As Viewed On CRT       .8         1.7.2-1       Opto-isolator Information       .9         1.7.3-1       Function Of The Schmitt Triggers       .10         1.7.4-1       Basic Multiplexer Logic Diagram       .10         1.7.4-2       Four-input Multiplexer Logic Diagram       .10         1.7.5-1       74175 Quad Latch Logic Diagram       .10         1.7.6-2       25510 Data Shifter Pin Configuration       .11         1.7.6-2       25510 Truth Table       .11         1.7.7-1       7442 Decoder Logic Diagram       .11         1.7.7-2       7442 Decoder Logic Diagram       .11         2.2.1-1       Game PCB Shifter Section<                      | 1.2.3- | Initial Play Mode Display2 |

| 1.3.5-1       Sound And Coins/Plays/Time Adjustments.       .3         1.4.1-1       System Block Diagram       .4         1.5.1-1       Mother PCB Block Diagram       .5         1.5.12-1       8080 CPU Block Diagram       .6         1.6.1-1       Game PCB Block Diagram       .7         1.6.2-1       Gun Arm Angle Code       .7         1.6.7-1       Word Locations During Shift       .8         1.6.7-2       Shift Process As Viewed On CRT       .8         1.7.2-1       Opto-isolator Information       .9         1.7.3-1       Function Of The Schmitt Triggers.       .10         1.7.4-1       Basic Multiplexer Logic Diagram       .10         1.7.4-2       Four-input Multiplexer Logic Diagram       .10         1.7.5-1       74175 Quad Latch Logic Diagram       .10         1.7.6-2       25S10 Data Shifter Pin Configuration       .11         1.7.6-2       25S10 Truth Table       .11         1.7.7-1       7442 Decoder Logic Diagram       .11         1.7.7-1       7442 Decoder Logic Diagram       .11         2.2.1-1       Game PCB Output Devices       .13         2.2.4-1       Sound Decode       .14         2.2.5-1       Video Image Generation       .1                               |        |                            |

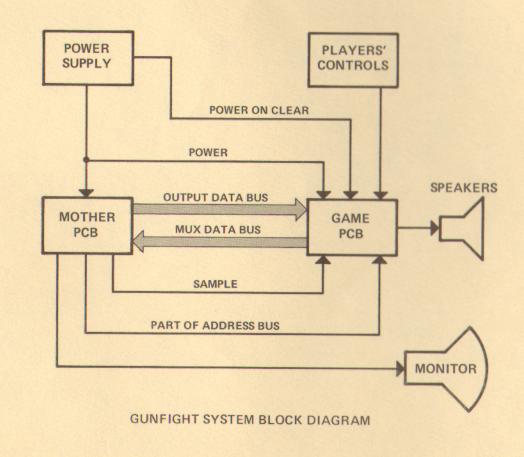

| 1.4.1-1       System Block Diagram       .4         1.5.1-1       Mother PCB Block Diagram       .5         1.5.12-1       8080 CPU Block Diagram       .6         1.6.1-1       Game PCB Block Diagram       .7         1.6.2-1       Gun Arm Angle Code       .7         1.6.7-1       Word Locations During Shift       .8         1.6.7-2       Shift Process As Viewed On CRT       .8         1.7.2-1       Opto-isolator Information       .9         1.7.3-1       Function Of The Schmitt Triggers       .10         1.7.4-1       Basic Multiplexer Logic Diagram       .10         1.7.4-2       Four-input Multiplexer Logic Diagram       .10         1.7.5-1       74175 Quad Latch Logic Diagram       .10         1.7.6-1       25S10 Data Shifter Pin Configuration       .11         1.7.6-2       25S10 Truth Table       .11         1.7.7-1       7442 Decoder Logic Diagram       .11         1.7.7-1       7442 Decoder Logic Diagram       .11         2.2.1-1       Game PCB Output Devices       .13         2.2.4-1       Sound Decode       .14         2.2.5-1       Video Image Generation       .15         2.6-2       15-Bit Latch Operation       .16                                                 |        |                            |

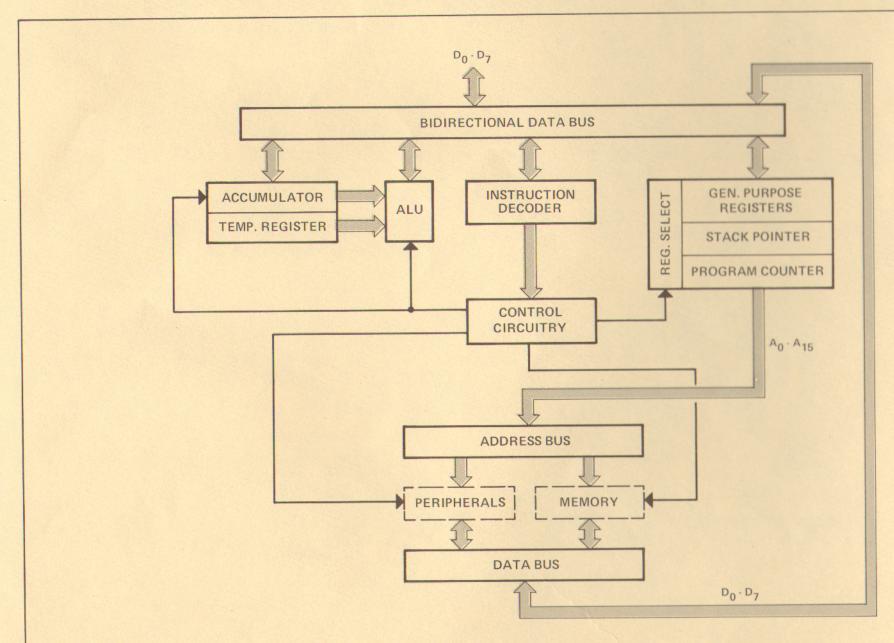

| 1.5.1-1       Mother PCB Block Diagram       .5         1.5.12-1       8080 CPU Block Diagram       .6         1.6.1-1       Game PCB Block Diagram       .7         1.6.2-1       Gun Arm Angle Code       .7         1.6.7-1       Word Locations During Shift       .8         1.6.7-2       Shift Process As Viewed On CRT       .8         1.7.2-1       Opto-isolator Information       .9         1.7.3-1       Function Of The Schmitt Triggers       .10         1.7.4-1       Basic Multiplexer Logic Diagram       .10         1.7.4-2       Four-input Multiplexer Logic Diagram       .10         1.7.5-1       74175 Quad Latch Logic Diagram       .10         1.7.6-2       25S10 Data Shifter Pin Configuration       .11         1.7.6-2       25S10 Truth Table       .11         1.7.7-1       7442 Decoder Logic Diagram       .11         1.7.7-1       7442 Decoder Logic Diagram       .11         2.2.1-1       Game PCB Output Devices       .13         2.2.4-1       Sound Decode       .14         2.2.5-1       Video Image Generation       .15         2.2.6-2       15-Bit Latch Operation       .16         2.2.6-3       Data Shifter Truth Table       .16     <                                    |        |                            |

| 1.5.12-1       8080 CPU Block Diagram       .6         1.6.1-1       Game PCB Block Diagram       .7         1.6.2-1       Gun Arm Angle Code       .7         1.6.7-1       Word Locations During Shift       .8         1.6.7-2       Shift Process As Viewed On CRT       .8         1.7.2-1       Opto-isolator Information       .9         1.7.3-1       Function Of The Schmitt Triggers       .10         1.7.4-1       Basic Multiplexer Logic Diagram       .10         1.7.4-2       Four-input Multiplexer Logic Diagram       .10         1.7.5-1       74175 Quad Latch Logic Diagram       .10         1.7.6-1       25S10 Data Shifter Pin Configuration       .11         1.7.6-2       25S10 Truth Table       .11         1.7.7-1       7442 Decoder Logic Diagram       .11         2.1.1-1       Power Supply Schematic       .12         2.2.1-1       Game PCB Output Devices       .13         2.2.4-1       Sound Decode       .14         2.2.5-1       Video Image Generation       .15         2.2.6-2       15-Bit Latch Operation       .16         2.2.8-1       Game PCB Input Section       .18         2.2.10-2       Gun Control Printed Circuit Board       .19                                     |        |                            |

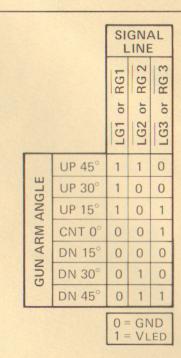

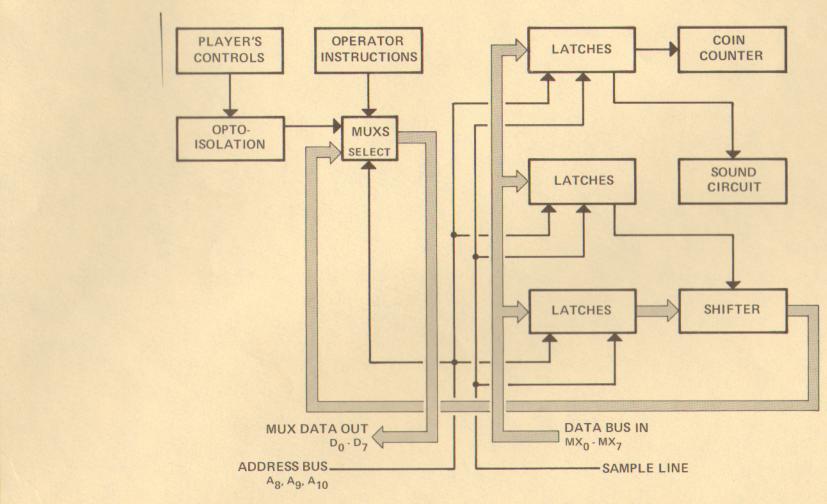

| 1.6.1-1       Game PCB Block Diagram       .7         1.6.2-1       Gun Arm Angle Code       .7         1.6.7-1       Word Locations During Shift       .8         1.6.7-2       Shift Process As Viewed On CRT       .8         1.7.2-1       Opto-isolator Information       .9         1.7.3-1       Function Of The Schmitt Triggers       .10         1.7.4-1       Basic Multiplexer Logic Diagram       .10         1.7.4-2       Four-input Multiplexer Logic Diagram       .10         1.7.5-1       74175 Quad Latch Logic Diagram       .10         1.7.6-1       25S10 Data Shifter Pin Configuration       .11         1.7.6-2       25S10 Truth Table       .11         1.7.7-1       7442 Decoder Logic Diagram       .11         2.1.1-1       Power Supply Schematic       .12         2.2.1-1       Game PCB Output Devices       .13         2.2.4-1       Sound Decode       .14         2.2.5-1       Video Image Generation       .15         2.2.6-2       15-Bit Latch Operation       .16         2.2.6-3       Data Shifter Truth Table       .16         2.2.8-1       Game PCB Input Section       .18         2.2.10-2       Multiplexed Game Data       .19                                               |        |                            |

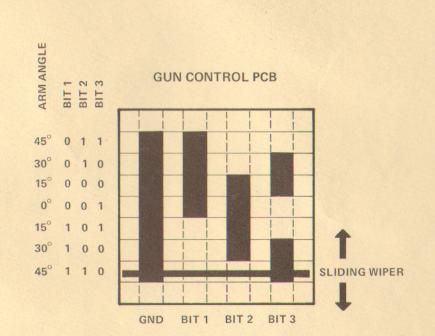

| 1.6.2-1       Gun Arm Angle Code       .7         1.6.7-1       Word Locations During Shift.       .8         1.6.7-2       Shift Process As Viewed On CRT       .8         1.7.2-1       Opto-isolator Information       .9         1.7.3-1       Function Of The Schmitt Triggers       .10         1.7.4-1       Basic Multiplexer Logic Diagram       .10         1.7.4-2       Four-input Multiplexer Logic Diagram       .10         1.7.5-1       74175 Quad Latch Logic Diagram       .10         1.7.6-1       25S10 Data Shifter Pin Configuration       .11         1.7.6-2       25S10 Truth Table       .11         1.7.7-1       7442 Decoder Logic Diagram       .11         1.7.7-1       7442 Decoder Logic Diagram       .11         2.1-1       Power Supply Schematic       .12         2.2.1-1       Game PCB Output Devices       .13         2.2.4-1       Sound Decode       .14         2.2.5-1       Video Image Generation       .15         2.2.6-1       Game PCB Shifter Section       .16         2.2.6-2       15-Bit Latch Operation       .16         2.2.6-3       Data Shifter Truth Table       .16         2.2.8-1       Game PCB Input Section       .18                                         |        |                            |

| 1.6.7-1       Word Locations During Shift.       .8         1.6.7-2       Shift Process As Viewed On CRT       .8         1.7.2-1       Opto-isolator Information       .9         1.7.3-1       Function Of The Schmitt Triggers       .10         1.7.4-1       Basic Multiplexer Logic Diagram       .10         1.7.4-2       Four-input Multiplexer Logic Diagram       .10         1.7.5-1       74175 Quad Latch Logic Diagram       .10         1.7.6-1       25S10 Data Shifter Pin Configuration       .11         1.7.6-2       25S10 Truth Table       .11         1.7.7-1       7442 Decoder Logic Diagram       .11         1.7.7-1       7442 Decoder Logic Diagram       .11         2.1.1-1       Power Supply Schematic       .12         2.2.1-1       Game PCB Output Devices       .13         2.2.4-1       Sound Decode       .14         2.2.5-1       Video Image Generation       .15         2.2.6-1       Game PCB Shifter Section       .16         2.2.6-2       15-Bit Latch Operation       .16         2.2.6-3       Data Shifter Truth Table       .16         2.2.8-1       Game PCB Input Section       .18         2.2.10-2       Gun Control Printed Circuit Board                                |        |                            |

| 1.6.7-2       Shift Process As Viewed On CRT       .8         1.7.2-1       Opto-isolator Information       .9         1.7.3-1       Function Of The Schmitt Triggers       .10         1.7.4-1       Basic Multiplexer Logic Diagram       .10         1.7.4-2       Four-input Multiplexer Logic Diagram       .10         1.7.5-1       74175 Quad Latch Logic Diagram       .10         1.7.6-1       25S10 Data Shifter Pin Configuration       .11         1.7.6-2       25S10 Truth Table       .11         1.7.7-1       7442 Decoder Logic Diagram       .11         2.1.1-1       Power Supply Schematic       .12         2.2.1-1       Game PCB Output Devices       .13         2.2.4-1       Sound Decode       .14         2.2.5-1       Video Image Generation       .15         2.2.6-1       Game PCB Shifter Section       .16         2.2.6-2       15-Bit Latch Operation       .16         2.2.8-1       Game PCB Input Section       .18         2.2.10-1       Multiplexed Game Data       .19         2.2.10-2       Gun Control Printed Circuit Board       .19         2.3.1-1       Sound Circuit Schematic       .20         2.3.2-1       Raw Noise Waveform (TP-4)       .                               |        |                            |

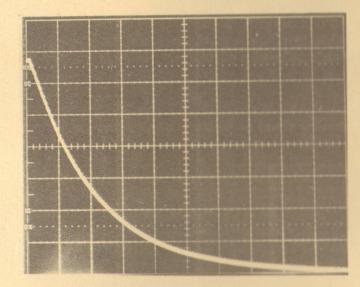

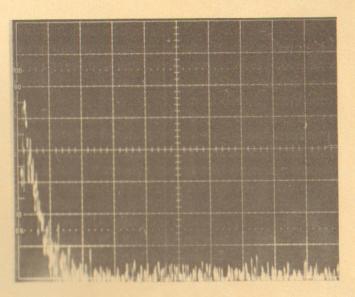

| 1.7.2-1       Opto-isolator Information       .9         1.7.3-1       Function Of The Schmitt Triggers       .10         1.7.4-1       Basic Multiplexer Logic Diagram       .10         1.7.4-2       Four-input Multiplexer Logic Diagram       .10         1.7.5-1       74175 Quad Latch Logic Diagram       .10         1.7.6-1       25S10 Data Shifter Pin Configuration       .11         1.7.6-2       25S10 Truth Table       .11         1.7.7-1       7442 Decoder Logic Diagram       .11         2.1.1-1       Power Supply Schematic       .12         2.2.1-1       Game PCB Output Devices       .13         2.2.4-1       Sound Decode       .14         2.2.5-1       Video Image Generation       .15         2.2.6-1       Game PCB Shifter Section       .16         2.2.6-2       15-Bit Latch Operation       .16         2.2.6-3       Data Shifter Truth Table       .16         2.2.8-1       Game PCB Input Section       .18         2.2.10-1       Multiplexed Game Data       .19         2.3.1-1       Sound Circuit Schematic       .20         2.3.2-1       Raw Noise Waveform (TP-4)       .21         2.3.2-2       Charging Of Shaping Capacitor (TP-6)       .21<                               |        |                            |

| 1.7.3-1       Function Of The Schmitt Triggers.       10         1.7.4-1       Basic Multiplexer Logic Diagram.       10         1.7.4-2       Four-input Multiplexer Logic Diagram.       10         1.7.5-1       74175 Quad Latch Logic Diagram.       10         1.7.6-1       25S10 Data Shifter Pin Configuration.       11         1.7.6-2       25S10 Truth Table.       11         1.7.7-1       7442 Decoder Logic Diagram.       11         2.1.1-1       Power Supply Schematic.       12         2.2.1-1       Game PCB Output Devices.       13         2.2.4-1       Sound Decode.       14         2.2.5-1       Video Image Generation.       15         2.2.6-1       Game PCB Shifter Section.       16         2.2.6-2       15-Bit Latch Operation.       16         2.2.6-3       Data Shifter Truth Table.       16         2.2.8-1       Game PCB Input Section.       18         2.2.10-1       Multiplexed Game Data.       19         2.3.1-1       Sound Circuit Schematic.       20         2.3.2-1       Raw Noise Waveform (TP-4)       21         2.3.2-2       Charging Of Shaping Capacitor (TP-6)       21         2.3.2-3       Resulting Noise Waveform (TP-7) <td< td=""><td></td><td></td></td<> |        |                            |

| 1.7.4-1       Basic Multiplexer Logic Diagram       10         1.7.4-2       Four-input Multiplexer Logic Diagram       10         1.7.5-1       74175 Quad Latch Logic Diagram       10         1.7.6-1       25S10 Data Shifter Pin Configuration       11         1.7.6-2       25S10 Truth Table       11         1.7.7-1       7442 Decoder Logic Diagram       11         2.1.1-1       Power Supply Schematic       12         2.2.1-1       Game PCB Output Devices       13         2.2.4-1       Sound Decode       14         2.2.5-1       Video Image Generation       15         2.2.6-1       Game PCB Shifter Section       16         2.2.6-2       15-Bit Latch Operation       16         2.2.6-3       Data Shifter Truth Table       16         2.2.8-1       Game PCB Input Section       18         2.2.10-1       Multiplexed Game Data       19         2.3.1-1       Sound Circuit Schematic       20         2.3.2-1       Raw Noise Waveform (TP-4)       21         2.3.2-2       Charging Of Shaping Capacitor (TP-6)       21         2.3.2-3       Resulting Noise Waveform (TP-7)       21         3.2.1-1       Test Point 1       22 <td></td> <td></td>                                             |        |                            |

| 1.7.4-2       Four-input Multiplexer Logic Diagram       10         1.7.5-1       74175 Quad Latch Logic Diagram       10         1.7.6-1       25S10 Data Shifter Pin Configuration       11         1.7.6-2       25S10 Truth Table       11         1.7.7-1       7442 Decoder Logic Diagram       11         2.1.1-1       Power Supply Schematic       12         2.2.1-1       Game PCB Output Devices       13         2.2.4-1       Sound Decode       14         2.2.5-1       Video Image Generation       15         2.2.6-1       Game PCB Shifter Section       16         2.2.6-2       15-Bit Latch Operation       16         2.2.6-3       Data Shifter Truth Table       16         2.2.8-1       Game PCB Input Section       18         2.2.10-1       Multiplexed Game Data       19         2.3.1-1       Sound Circuit Schematic       20         2.3.2-1       Raw Noise Waveform (TP-4)       21         2.3.2-2       Charging Of Shaping Capacitor (TP-6)       21         2.3.2-3       Resulting Noise Waveform (TP-7)       21         3.2.1-1       Test Point 1       22                                                                                                                                |        |                            |

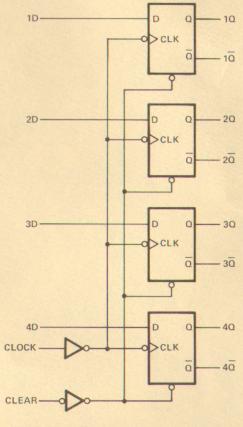

| 1.7.5-1       74175 Quad Latch Logic Diagram.       10         1.7.6-1       25S10 Data Shifter Pin Configuration.       11         1.7.6-2       25S10 Truth Table.       11         1.7.7-1       7442 Decoder Logic Diagram.       11         2.1.1-1       Power Supply Schematic.       12         2.2.1-1       Game PCB Output Devices.       13         2.2.4-1       Sound Decode.       14         2.2.5-1       Video Image Generation.       15         2.2.6-1       Game PCB Shifter Section.       16         2.2.6-2       15-Bit Latch Operation.       16         2.2.6-3       Data Shifter Truth Table.       16         2.2.8-1       Game PCB Input Section.       18         2.2.10-1       Multiplexed Game Data.       19         2.2.10-2       Gun Control Printed Circuit Board.       19         2.3.1-1       Sound Circuit Schematic.       20         2.3.2-1       Raw Noise Waveform (TP-4).       21         2.3.2-2       Charging Of Shaping Capacitor (TP-6).       21         2.3.2-3       Resulting Noise Waveform (TP-7).       21         3.2.1-1       Test Point 1.       22                                                                                                               |        |                            |

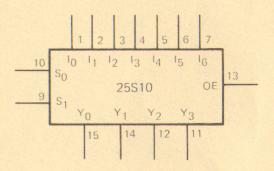

| 1.7.6-1       25S10 Data Shifter Pin Configuration       11         1.7.6-2       25S10 Truth Table       11         1.7.7-1       7442 Decoder Logic Diagram       11         2.1.1-1       Power Supply Schematic       12         2.2.1-1       Game PCB Output Devices       13         2.2.4-1       Sound Decode       14         2.2.5-1       Video Image Generation       15         2.2.6-1       Game PCB Shifter Section       16         2.2.6-2       15-Bit Latch Operation       16         2.2.6-3       Data Shifter Truth Table       16         2.2.8-1       Game PCB Input Section       18         2.2.10-1       Multiplexed Game Data       19         2.2.10-2       Gun Control Printed Circuit Board       19         2.3.1-1       Sound Circuit Schematic       20         2.3.2-1       Raw Noise Waveform (TP-4)       21         2.3.2-2       Charging Of Shaping Capacitor (TP-6)       21         2.3.2-3       Resulting Noise Waveform (TP-7)       21         3.2.1-1       Test Point 1       22                                                                                                                                                                                                |        |                            |

| 1.7.6-2       25S10 Truth Table       11         1.7.7-1       7442 Decoder Logic Diagram       11         2.1.1-1       Power Supply Schematic       12         2.2.1-1       Game PCB Output Devices       13         2.2.4-1       Sound Decode       14         2.2.5-1       Video Image Generation       15         2.2.6-1       Game PCB Shifter Section       16         2.2.6-2       15-Bit Latch Operation       16         2.2.6-3       Data Shifter Truth Table       16         2.2.8-1       Game PCB Input Section       18         2.2.10-1       Multiplexed Game Data       19         2.3.1-1       Sound Circuit Schematic       20         2.3.2-1       Raw Noise Waveform (TP-4)       21         2.3.2-2       Charging Of Shaping Capacitor (TP-6)       21         2.3.2-3       Resulting Noise Waveform (TP-7)       21         3.2.1-1       Test Point 1       22                                                                                                                                                                                                                                                                                                                                      |        |                            |

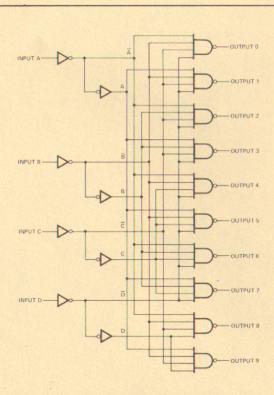

| 1.7.7-1       7442 Decoder Logic Diagram       11         2.1.1-1       Power Supply Schematic       12         2.2.1-1       Game PCB Output Devices       13         2.2.4-1       Sound Decode       14         2.2.5-1       Video Image Generation       15         2.2.6-1       Game PCB Shifter Section       16         2.2.6-2       15-Bit Latch Operation       16         2.2.6-3       Data Shifter Truth Table       16         2.2.8-1       Game PCB Input Section       18         2.2.10-1       Multiplexed Game Data       19         2.3.1-1       Sound Circuit Schematic       20         2.3.2-1       Raw Noise Waveform (TP-4)       21         2.3.2-2       Charging Of Shaping Capacitor (TP-6)       21         2.3.2-3       Resulting Noise Waveform (TP-7)       21         3.2.1-1       Test Point 1       22                                                                                                                                                                                                                                                                                                                                                                                       |        |                            |

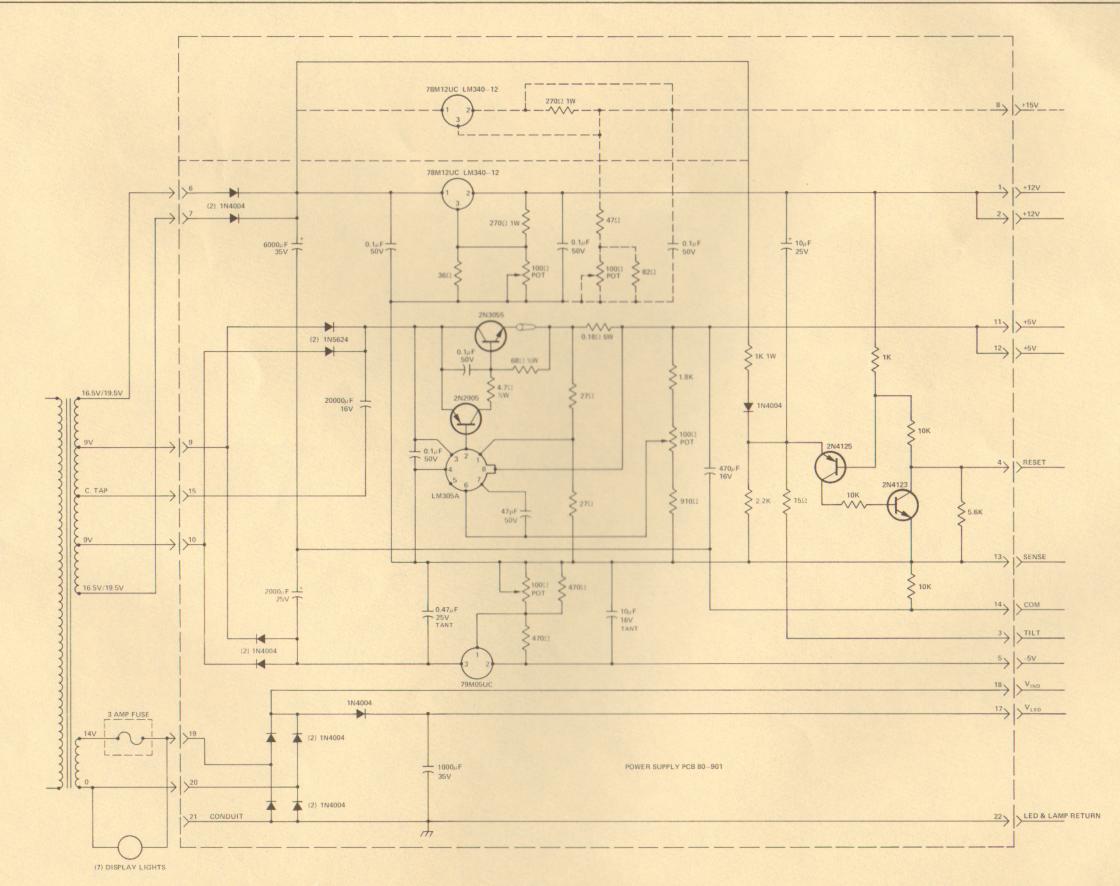

| 2.1.1-1       Power Supply Schematic.       12         2.2.1-1       Game PCB Output Devices       13         2.2.4-1       Sound Decode       14         2.2.5-1       Video Image Generation       15         2.2.6-1       Game PCB Shifter Section       16         2.2.6-2       15-Bit Latch Operation       16         2.2.6-3       Data Shifter Truth Table       16         2.2.8-1       Game PCB Input Section       18         2.2.10-1       Multiplexed Game Data       19         2.3.1-1       Sound Circuit Schematic       20         2.3.2-1       Raw Noise Waveform (TP-4)       21         2.3.2-2       Charging Of Shaping Capacitor (TP-6)       21         2.3.2-3       Resulting Noise Waveform (TP-7)       21         3.2.1-1       Test Point 1       .22                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |                            |

| 2.2.1-1       Game PCB Output Devices       13         2.2.4-1       Sound Decode       14         2.2.5-1       Video Image Generation       15         2.2.6-1       Game PCB Shifter Section       16         2.2.6-2       15-Bit Latch Operation       16         2.2.6-3       Data Shifter Truth Table       16         2.2.8-1       Game PCB Input Section       18         2.2.10-1       Multiplexed Game Data       19         2.3.1-1       Sound Circuit Schematic       20         2.3.2-1       Raw Noise Waveform (TP-4)       21         2.3.2-2       Charging Of Shaping Capacitor (TP-6)       21         2.3.2-3       Resulting Noise Waveform (TP-7)       21         3.2.1-1       Test Point 1       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |                            |

| 2.2.4-1       Sound Decode       14         2.2.5-1       Video Image Generation       15         2.2.6-1       Game PCB Shifter Section       16         2.2.6-2       15-Bit Latch Operation       16         2.2.6-3       Data Shifter Truth Table       16         2.2.8-1       Game PCB Input Section       18         2.2.10-1       Multiplexed Game Data       19         2.2.10-2       Gun Control Printed Circuit Board       19         2.3.1-1       Sound Circuit Schematic       20         2.3.2-1       Raw Noise Waveform (TP-4)       21         2.3.2-2       Charging Of Shaping Capacitor (TP-6)       21         2.3.2-3       Resulting Noise Waveform (TP-7)       21         3.2.1-1       Test Point 1       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |                            |

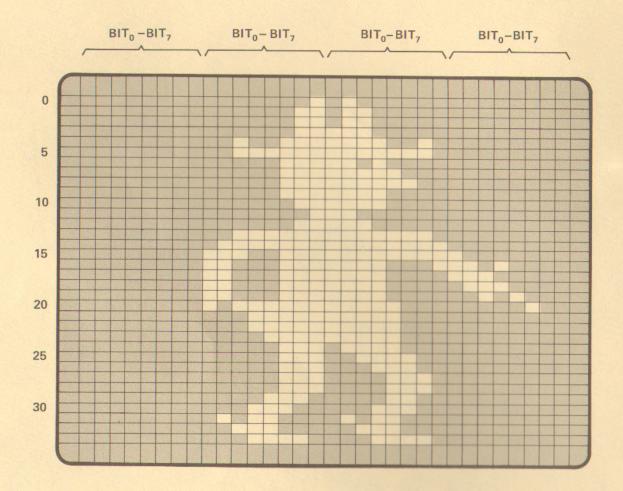

| 2.2.5-1       Video Image Generation       15         2.2.6-1       Game PCB Shifter Section       16         2.2.6-2       15-Bit Latch Operation       16         2.2.6-3       Data Shifter Truth Table       16         2.2.8-1       Game PCB Input Section       18         2.2.10-1       Multiplexed Game Data       19         2.2.10-2       Gun Control Printed Circuit Board       19         2.3.1-1       Sound Circuit Schematic       20         2.3.2-1       Raw Noise Waveform (TP-4)       21         2.3.2-2       Charging Of Shaping Capacitor (TP-6)       21         2.3.2-3       Resulting Noise Waveform (TP-7)       21         3.2.1-1       Test Point 1       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |                            |

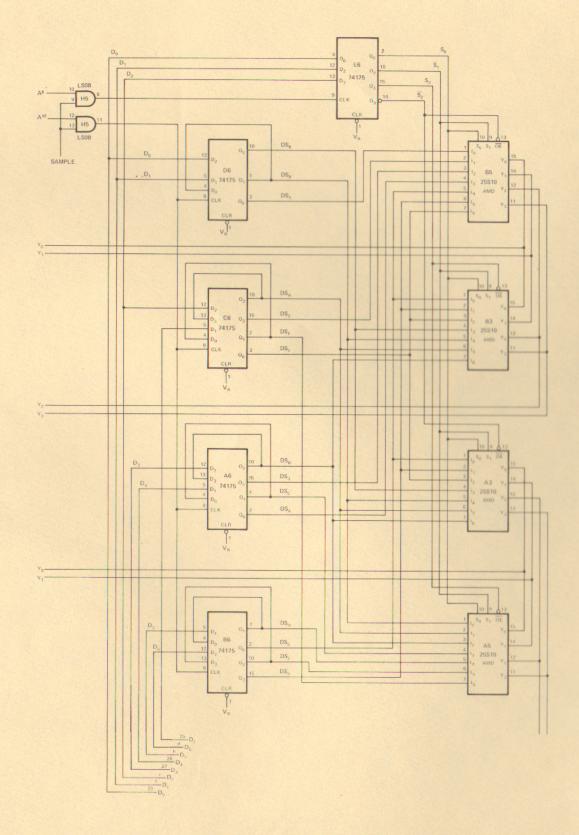

| 2.2.6-1       Game PCB Shifter Section.       16         2.2.6-2       15-Bit Latch Operation.       16         2.2.6-3       Data Shifter Truth Table.       16         2.2.8-1       Game PCB Input Section.       18         2.2.10-1       Multiplexed Game Data.       19         2.2.10-2       Gun Control Printed Circuit Board       19         2.3.1-1       Sound Circuit Schematic.       20         2.3.2-1       Raw Noise Waveform (TP-4)       21         2.3.2-2       Charging Of Shaping Capacitor (TP-6)       21         2.3.2-3       Resulting Noise Waveform (TP-7)       21         3.2.1-1       Test Point 1       .22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |                            |

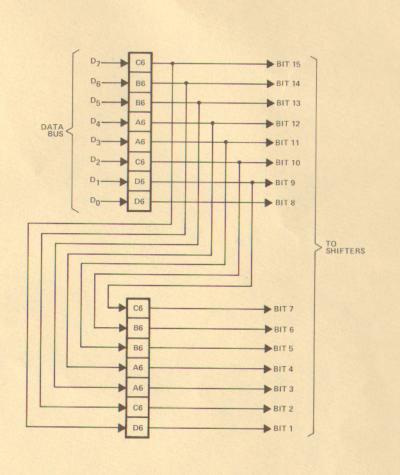

| 2.2.6-2       15-Bit Latch Operation       16         2.2.6-3       Data Shifter Truth Table       16         2.2.8-1       Game PCB Input Section       18         2.2.10-1       Multiplexed Game Data       19         2.2.10-2       Gun Control Printed Circuit Board       19         2.3.1-1       Sound Circuit Schematic       20         2.3.2-1       Raw Noise Waveform (TP-4)       21         2.3.2-2       Charging Of Shaping Capacitor (TP-6)       21         2.3.2-3       Resulting Noise Waveform (TP-7)       21         3.2.1-1       Test Point 1       .22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |                            |

| 2.2.6-3       Data Shifter Truth Table       16         2.2.8-1       Game PCB Input Section       18         2.2.10-1       Multiplexed Game Data       19         2.2.10-2       Gun Control Printed Circuit Board       19         2.3.1-1       Sound Circuit Schematic       20         2.3.2-1       Raw Noise Waveform (TP-4)       21         2.3.2-2       Charging Of Shaping Capacitor (TP-6)       21         2.3.2-3       Resulting Noise Waveform (TP-7)       21         3.2.1-1       Test Point 1       .22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |                            |

| 2.2.8-1       Game PCB Input Section.       18         2.2.10-1       Multiplexed Game Data.       19         2.2.10-2       Gun Control Printed Circuit Board       19         2.3.1-1       Sound Circuit Schematic.       20         2.3.2-1       Raw Noise Waveform (TP-4)       21         2.3.2-2       Charging Of Shaping Capacitor (TP-6)       21         2.3.2-3       Resulting Noise Waveform (TP-7)       21         3.2.1-1       Test Point 1       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |                            |

| 2.2.10-1       Multiplexed Game Data.       .19         2.2.10-2       Gun Control Printed Circuit Board       .19         2.3.1-1       Sound Circuit Schematic.       .20         2.3.2-1       Raw Noise Waveform (TP-4)       .21         2.3.2-2       Charging Of Shaping Capacitor (TP-6)       .21         2.3.2-3       Resulting Noise Waveform (TP-7)       .21         3.2.1-1       Test Point 1       .22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |                            |

| 2.2.10-2       Gun Control Printed Circuit Board       .19         2.3.1-1       Sound Circuit Schematic       .20         2.3.2-1       Raw Noise Waveform (TP-4)       .21         2.3.2-2       Charging Of Shaping Capacitor (TP-6)       .21         2.3.2-3       Resulting Noise Waveform (TP-7)       .21         3.2.1-1       Test Point 1       .22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |                            |

| 2.3.1-1       Sound Circuit Schematic       .20         2.3.2-1       Raw Noise Waveform (TP-4)       .21         2.3.2-2       Charging Of Shaping Capacitor (TP-6)       .21         2.3.2-3       Resulting Noise Waveform (TP-7)       .21         3.2.1-1       Test Point 1       .22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |                            |

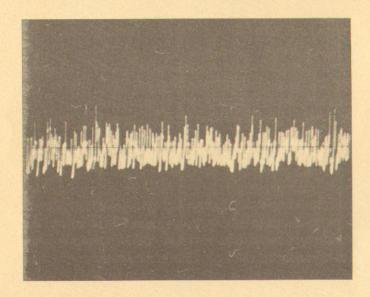

| 2.3.2-1       Raw Noise Waveform (TP-4)       .21         2.3.2-2       Charging Of Shaping Capacitor (TP-6)       .21         2.3.2-3       Resulting Noise Waveform (TP-7)       .21         3.2.1-1       Test Point 1       .22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |                            |

| 2.3.2-2       Charging Of Shaping Capacitor (TP-6).       .21         2.3.2-3       Resulting Noise Waveform (TP-7).       .21         3.2.1-1       Test Point 1.       .22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |                            |

| 2.3.2-3       Resulting Noise Waveform (TP-7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |                            |

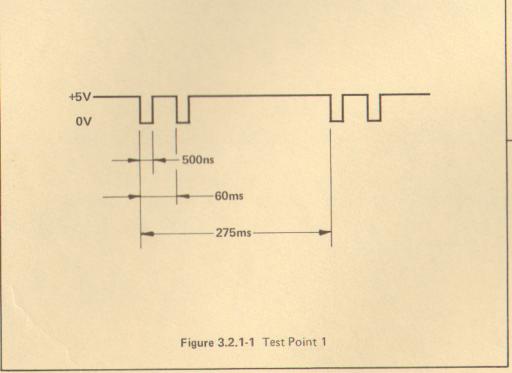

| 3.2.1-1 Test Point 122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |                            |

| 3.2.5-1 Test Point 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |                            |

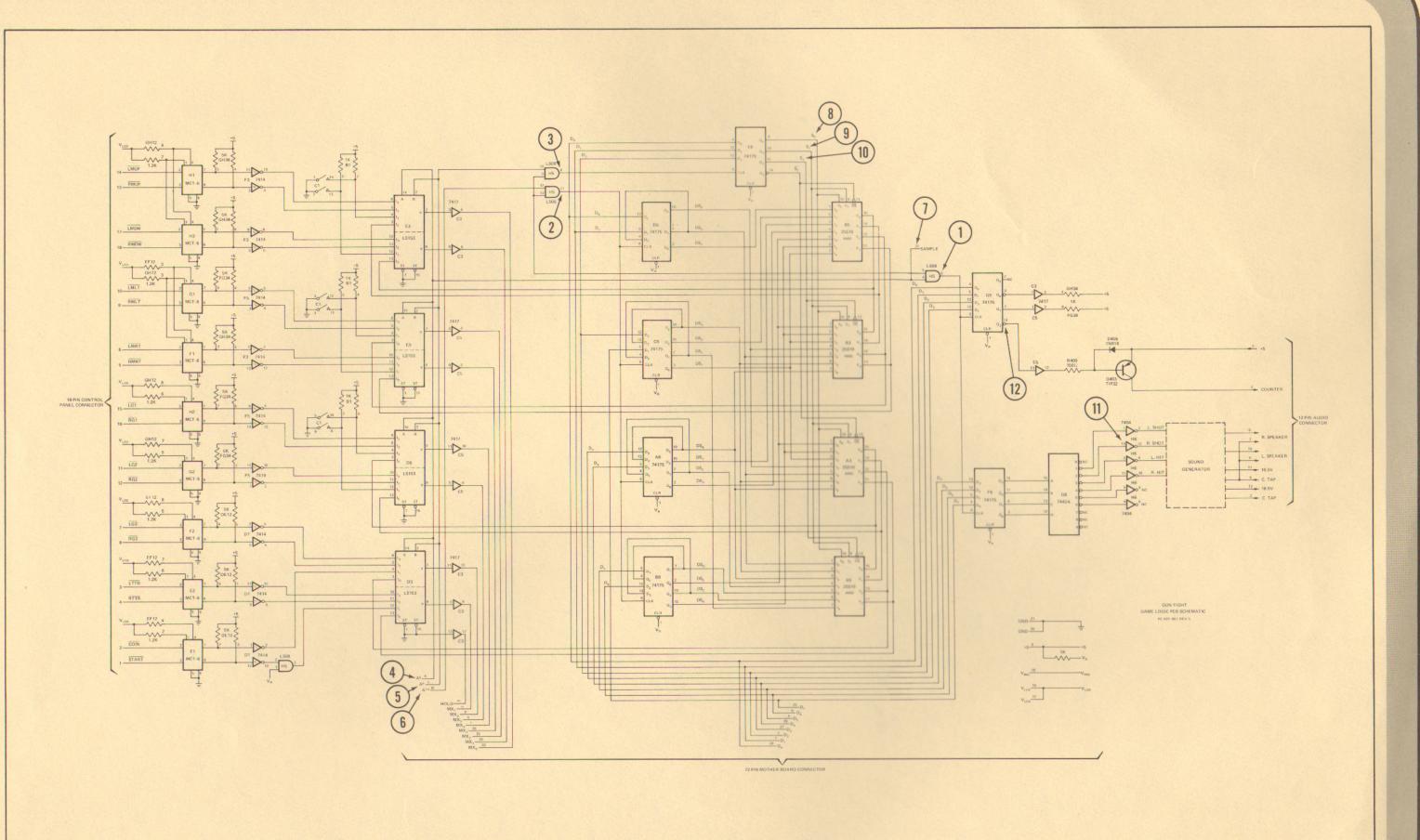

| 1.1.1-1 Gun Fight Digital Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |                            |

#### SECTION I GENERAL INFORMATION

#### 1.1 Introduction

1.1.1 Why Use A Microprocessor? The integrated microprocessor (often abbreviated simply as  $\mu P$ ) has caused a revolution in the electronics industry for the contemporary µP now makes possible real computers for only a few hundred dollars. Ever since the advent of video games, designers have often wanted to use an actual, general-purpose type computer to operate their games and, in fact, a few custom games have been constructed using fairly powerful minicomputers. But it has never been possible to use such a computer for production video games simply because the cheapest available minicomputers cost thousands, rather than hundreds, of dollars. But today, with micoprocessor chips available for \$20 and under, systems comparable in power to commercial minis can be built for maybe a tenth of the cost. Obviously the  $\mu P$  is a reality today and is rapidly changing the face of the electronics industry. But what of the reasons designers are so interested in applying them to video games? After all, video games have been successfully manufactured for a number of years using the random-logic type of architecture, so why change now?

Actually, there are quite a few reasons, but most of them boil down to two considerations: economics and design flexibility. But before getting into all of this, let's take a couple of steps backwards and talk about earlier techniques for implementing video game designs.

1.1.2 Random Logic Vs. Processor Control. Before  $\mu P$  systems burst upon the scene, video games were invariably designed using a dedicated "computer" custom built from random-logic elements which are assembled in such a way as to generate both the video images displayed on the screen and the various rules by which these images are controlled. The typical random-logic video game computer consists of a large number of SSI and MSI devices wired together to produce the desired effects. Since only small and medium scale devices are used, this type of computer tends to require a large amount of circuitry and PCB real estate to generate even the simplest displays and algorithms.

While the random-logic approach clearly works, it has several serious drawbacks which become particularly evident when this technique is compared with operating a game via processor control. Probably the most significant disadvantage is the tremendous amount of development time required to generate each new game since an entirely new computer is required for every distinctly different game theme. Furthermore, bugs which show up in the field at a later date can become a serious problem and one which may be extremely difficult to correct since all the boards must be recalled from all over the country (or even all over the world) and the custom printed circuit board modified by cutting traces and adding jumpers to implement the engineering change.

Now, compare this with the way a microprocessor game is developed.

First, the central processing unit (CPU) is designed. Although the CPU may not contain a very large chip count as compared with a random-logic design, be aware that many of the chips found on a CPU board are LSI circuits which contain many more individual components than the simpler MSI varieties. So, although the physical size of the CPU circuitry may be smaller, the overall complexity of the system is far greater.

Microprocessor manufacturers not only build the  $\mu P$  itself, but they also generate associated componentry necessary to the operation of the microprocessor chip. A good example is the 8216 Bidirectional I/O Driveers used to control the 8080 system data bus. These chips are absolutely necessary to the operation of the 8080 and the manufacturer of the devices also supplies the schematic for their connection. Furthermore, almost all  $\mu P$  manufacturers also supply a developmental system which the engineer can often use to "breadboard" his design. In fact, sometimes all that the engineer really needs to do is to write his own custom program and eliminate any unnecessary circuitry from the developmental system. Actually, the system is already half designed before the video game designer sits down and starts work and this can obviously result in a tremendous savings of engineering time.

So, after playing with the developmental system for a while, the designer creates the actual CPU design for the video game while taking into consideration the types of functions the game system will need to perform. One of the major considerations is the fact that the CPU must work for a large number of different game themes. If the system is in fact designed according to this consideration, it should be useful for an extended period of time and this is the main reason the µP architecture is so attractive, for once the company has a viable design, a number of advantages are guickly realized. Obviously, the most important is the fact that the development costs required to get the initial system up can be spread out over the entire run of machines which might last for several years. Furthermore, only a relatively small number of parts need be stocked at a considerable savings to the manufacturer. And, since the manufacturer knows a great many CPU boards will be sold during the production run, a large number of them can be produced at once which greatly reduces the costs involved in making high quality printed circuit boards. For example, one of the larger costs associated with manufacturing PC boards is setting up for drilling. Obviously, the more boards that are drilled, the cheaper the set-up cost for each board will be.

But there are many more advantages with the  $\mu P$  architecture other than savings realized in engineering and the actual construction of the PCBs. Prior to shipping, all boards must be thoroughly tested and since a single CPU system is used for a great many different games themes, there is no need for test technicians to become familiar with a new random-logic design every month or so.

1.1.3 Advantages of Software Control. The foregoing examples have all been hardware-oriented advantages, but what we are really dealing with here is a software-oriented system wherein the software itself offers a great many benefits which may or may not be immediately obvious. For example, once a reliable CPU has been created, implementing another game theme mainly becomes a matter of writing new software and this can often be accomplished in a tenth of the time that would ordinarily be required to assemble a new hard-wired, random-logic design. Also, if bugs show up in the new game, these can be worked out on a

software level in such a way that the program is corrected and shipped out at only a fraction of what it would take to recall a large number of random-logic PCBs and modify them to correct the problem.

Software systems are quite flexible and this aspect offers a number of advantages not possible with random-logic designs. For instance, several objects can be moved on the CRT simultaneously using a  $\mu P$  without increasing system complexity. However, were a designer to try to do this with a random-logic game, he would quickly discover that he needs a separate motion circuit for each different image to be moved. Were he to want very much action on the CRT, he could easily end up with a game not feasible to produce with random-logic elements.

Software controlled video games are more easily modified in the field and this could conceivably be of great significance depending on the actual circumstances. Sometimes a game looks very good in a test situation, but receives little play in the field. Were the manufacturer not able to correct this situation, that company could encounter trouble. However, if the game happened to be a software oriented system, the manufacturer could still rectify the situation even after the games had been shipped from the factory for all the company needs to do to correct the matter is to write a more acceptable game program, burn it into a number of PROMs and send them out free of charge to the disappointed operators.

And lastly, once people become used to a particular  $\mu P$  system, technicians everywhere will be able to repair games using that system. Also, since most  $\mu Ps$  function similarly, there is a great deal of positive tranference from one system to another meaning that technicians will already be acquainted with the general architecture of the system before they sit down and become familiar with the specifics of that system.

Now that we have discussed some of the reasons that microprocessors are so quickly gaining in popularity for video games (and a tremendous number of other systems as well), it is time to turn our attention to the specifics of the Gunfight game system. In the following pages, we will discuss the general architecture of the Midway 8080 CPU mother board and the Gunfight game board as well as the specific operation of all phases and components of the system itself. In conclusion, we will present a number of troubleshooting approaches for dealing with specific problems and problematic areas as well as providing a generous amount of actual troubleshooting data so that video game technicians with ordinary troubleshooting equipment will be able to fully explore the circuitry found in this game.

# 1.2 A Typical Game Sequence

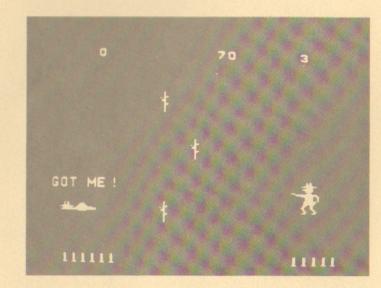

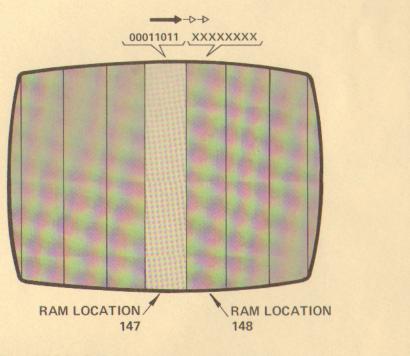

1.2.1 The Attract Mode. The condition of the game prior to the start of the game is known as the attract mode and this mode is characterized by the display in Figure 1.2.1-1. During the attract mode, the left cowboy simply walks onto the screen, fires a shot and retreats again only to repeat the same process a few seconds later. The name of the game (Gun Fight), the score remaining from the last game (0 0) and the announcement that the game has ended (Game Over) are dispalyed on the CRT as well. And, since the function of the attract mode is to entice prospective

players into depositing their coins, the words "Insert Coin" are placed on the screen.

Figure 1.2.1-1 Attract Mode Display

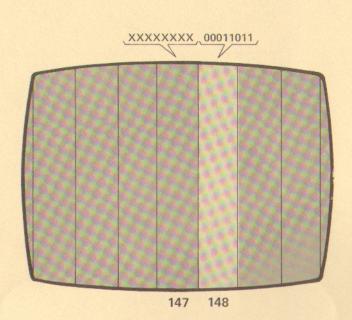

**1.2.2 The Credit Mode.** After the players have deposited a coin, the CRT announces, "Hey pardner! You have credit. Push (start) button." The game will not commence until the start button is pressed.

Figure 1.2.2-1 Credit Mode Display

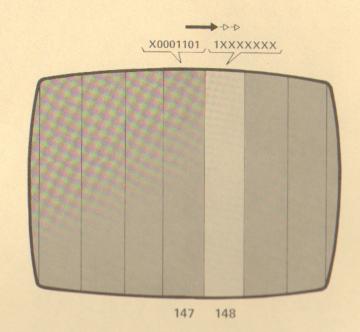

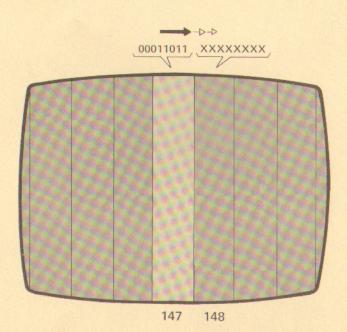

1.2.3 The Play Mode. After pressing the start button, the game begins. At this point, the players' controls become "live" and each player discovers that he can move his cowboy in any direction within his playing area, that he can control the position of his cowboy's gun arm and that he can fire a shot from his gun.

In addition to the two cowboys, a number of other images are displayed on the CRT. Under each cowboy is a series of symbolized shells or bullets and, as with a real "six-shooter," each cowboy is allowed only six shots per shoot-out. As each shot is fired, one of the bullet images is removed from the bottom of the screen. Also displayed at this time are the game timer (center numerals) and each player's individual score (left and right numerals).

Figure 1.2.3-1 Initial Play Mode Display

When one cowboy shoots the other, the cowboy who is hit falls down into a prone position, the words "Got me" are displayed above the body and the cowboy's hat is placed over his face (Figure 1.2.3-2). Simultaneously, the successful player is awarded a point for scoring the hit and this is indicated by incrementing his set of score numerals.

If one cowboy uses up all his ammunition without hitting the opposing cowboy, the shoot-out timer begins counting down. The shoot-out timer is located midway between the left player's score and the game timer. When this timer reaches zero, a new shoot-out is automatically started by the computer.

Figure 1.2.3-2 "Got Me" Display

The game continues in this fashion until the game timer is decremented down to zero, however, after each shoot-out an additional object is placed on the screen to increase the difficulty of the game. The first object is a single cactus, to which a second cactus is added at the next shoot-out, and so on until several cacti, pine trees and a moving stage-coach are all displayed on the CRT at the same time.

It is interesting to note that each player is given his own set of objects which he can hide behind safely without fear of being shot. For example, the left player can hide behind the left pine tree and also shoot through this pine tree. But if the right player tries to shoot the left player through the left tree, his shot will only blow off a small piece of the tree and not hit the left player. The stagecoach is an object which is held in common for both players in that neither player is able to shoot through the stagecoach.

### 1.3 Electrical Adjustments

1.3.1 Introduction. In this system, there are four main categories of electrical adjustments and these are: (1) TV monitor adjustments, (2) power supply adjustments, (3) operator adjustments and (4) sound system adjustments.

1.3.2 TV Monitor Adjustments. These adjustments are located on the TV monitor itself where the four most commonly used ones (A-D) are found on a panel accessable from the rear of the monitor. Vertical liniarity and height are adjusted via pots located on a printed circuit board in the monitor and the yoke is adjusted at the rear of the picture tube. More detailed information concerning the locations of these adjustments is found in the Motorola monitor manual.

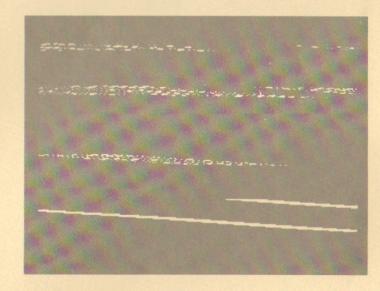

A. HORIZONTAL HOLD: Adjustment is indicated only if the picture is off center horizontally, if the images appear warped or if the entire picture is broken up into a series of diagonal lines (Figure 1.3.2-1). Adjust for a stable, horizontally centered picture.

Figure 1.3.2-1 Horizontal Hold Adjustment Will Generally Rectify This Problem

- B. VERTICAL HOLD: Adjustment is indicated if the picture appears to be rolling up or down the CRT or if the picture is stable, but not centered vertically. Adjust for a stable, vertically centered picture.

- C. BRIGHTNESS: Brightness is adjusted before contrast. Adjust for a dark background.

- D. CONTRAST: Adjust so the white images are as bright as possible against the dark background without being blurred.

- E. VERTICAL LINIARITY: Adjust only if the images at the top of the CRT appear to be compressed. If adjustment is indicated, adjust the V LIN pot so that the stagecoach image does not become compressed as it travels from the bottom to the top of the CRT.

- F. VERTICAL HEIGHT: Adjust only if the entire picture appears compressed vertically. Be aware that there is some interdependence between the liniarity and height adjustments.

- G. YOKE: Yoke adjustment is indicated only if the entire picture is off center and the H HOLD adjustment has insufficient effect. Adjust both yoke rings simultaneously for optimum centering of the image area within the borders of the CRT.

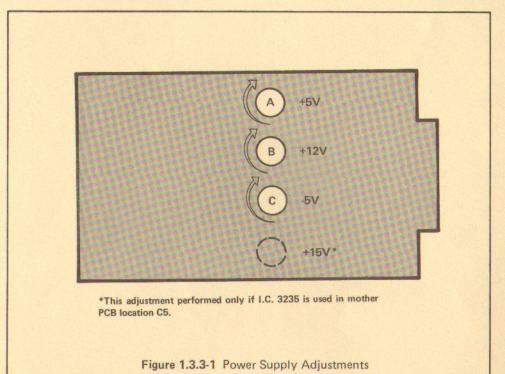

- **1.3.3 Power Supply Adjustments.** The following power supply adjustments are performed at the power supply PCB (P.C. 80-901) and the specific adjustment locations are indicated in Figure 1.3.3-1. Arrows indicate direction of increase.

A. +5 VOLT SUPPLY: Connect a VOM or DVM to power PCB edge connector pin 11 (or 12) and ground and adjust pot A for a reading of exactly +5 volts.

- B. +12 VOLT SUPPLY: Connect test instrument to power PCB edge connector pin 1 (or 2) and ground and adjust pot B for a reading of exactly +12 volts.

- C. -5 VOLT SUPPLY: Connect test instrument to power PCB edge connector pin 5 and ground and adjust pot C for a reading of exactly -5 volts.

- D. +15 VOLT SUPPLY: Perform this adjustment only if 3235 clock driver is found at mother PCB location C5. Connect test instrument between pin 8 of the power PCB edge connector and ground and adjust pot D for a reading of exactly +15 volts.

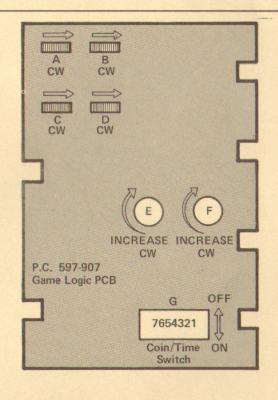

- 1.3.4 Operator Adjustments. These adjustments are performed by setting individual on/off switches found in a DIP package located at game PCB position C1 (see Figure 1.3.5-1). The following adjustments affect game length, plays per game, credit and coins required for game credit. Please be aware that the adjustment procedure varies according to game PCB revision number. If the game PCB carries the revision number 597-907B, use the information in the center columns. If the PCB carries revision number 597-907C, D or E, use the information under the right columns.

- A. GAME TIME: To adjust the total number of time units per game, set the switches according to the table below. For example, if you have a B revision game PCB and you desire a game length of 90 time units, set switches 2 and 3 to the OFF position.

| TIME     | PCB 597-907B<br>SW#2 SW#3 | PCB 597-907C,D&E<br>SW#5 SW#6 |

|----------|---------------------------|-------------------------------|

| 90 UNITS | OFF OFF                   | OFF OFF                       |

| 80 UNITS | OFF ON                    | ON OFF                        |

| 70 UNITS | ON OFF                    | OFF ON                        |

| 60 UNITS | ON ON                     | ON ON                         |

B. COINS PER GAME CREDIT: This procedure adjusts the number of coins required to produce game credit. Please be aware that game credit may allow the player 1 to 4 games depending on how the next adjustment procedure is performed. Adjust according to the table below. For example, if 1 coin per credit is desired for a B revision game PCB, set switches 4 and 6 to the ON position.

| NUMBER OF COINS    | PCB 597-907B<br>SW#4 SW#6 |            |                | 3 597-9<br>SW#1 | 07C, D&E<br>SW#2 |

|--------------------|---------------------------|------------|----------------|-----------------|------------------|

| 4 COINS<br>3 COINS | OFF<br>ON                 | OFF<br>OFF | NO STORY       | OFF<br>ON       | OFF<br>OFF       |

| 2 COINS<br>1 COIN  | OFF<br>ON                 | ON<br>ON   | DE DESTRUCTION | OFF             | ON<br>ON         |

C. PLAYS PER GAME CREDIT: This procedure adjusts the number of games awarded the player once game credit has been achieved. Adjust according to the table below. For example, if 1 play per game credit is

desired adjust switches 5 and 7 to the ON position if you have a B revision game PCB.

| NUMBER OF PLAYS                                                      | 597-9<br>SW#5          | The second secon | 597-907C, D&E<br>SW#3 SW#4 |  |  |